# O início do ensino de circuitos VLSI em Portugal

### O Conceito do Chip Multiprojeto (CMP)

Em 1966, Robert W. Bower [1], desenvolve uma técnica de fabricação de circuitos com transístores MOS em que a porta funciona como máscara para a fonte e o dreno, realizados por implantação iónica, proporcionando o auto alinhamento da porta, o que viria a revolucionar o projeto de circuitos VLSI.

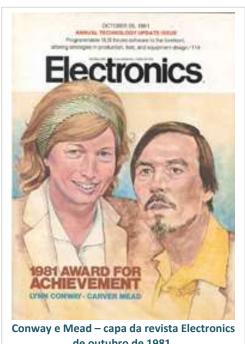

Em 1970, Carver Mead, professor da Caltech EUA ensinou, pela primeira vez, um curso de projeto de circuitos integrados de grande dimensão usando a tecnologia de transístores de efeito de campo NMOS. Mead foi o principal divulgador da célebre regra de Moore<sup>1</sup>, estabelecida em 1965, que previa a rápida evolução desta tecnologia. Mead desenvolveu técnicas de projeto que podiam ser escaláveis e aplicadas para novas evoluções da tecnologia. Em 1975, Mead começou a colaborar com a cientista Linn Conway investigadora do PARC<sup>2</sup> da empresa Xerox. Linn Conway entusiasmou-se com as perspetivas de evolução desta tecnologia e com as regras escaláveis e Mead. Mead and Conway começaram a trabalhar num livro que revolucionaria o projeto de circuitos integrados NMOS. Em 1978, Conway teve um enorme sucesso no curso de VLSI, no M.I.T. (EUA), usando as técnicas e regras desenvolvidas por ambos. Em 1979, publicaram o livro "Introduction to VLSI Systems" [2], que teve sucesso mundial imediato. Pela primeira vez os estudantes podiam projetar circuitos na universidade e ter acesso a informação que até então estava restrita às empresas do setor.

de outubro de 1981.

Em 1979, Mead e Conway obtiveram financiamento da DARPA<sup>3</sup> e criaram o primeiro projeto colaborativo de realização de circuitos integrados monolíticos em que participaram várias universidades dos Estados Unidos da América, seguindo as metodologias simples que propuseram. O projeto designado por MPC79, "Multi Project Chip 79", teve um enorme sucesso: participaram mais de uma dúzia de universidades, 124 investigadores com 82 projetos de circuitos diferentes.

Mead e Conway divulgaram mundialmente este novo conceito de projeto e o conceito do MPC79 foi rapidamente replicado em França, em 1981 e, na Alemanha, em 1983.

Em 1981, François Anceau, o pai da microeletrónica francesa, e Alain Guyot, apenas 18 meses depois do MCP79, projetaram, em França, os três primeiros chips usando os conceitos de Mead e Conway.

### O primeiro CMP português

Em 1982, em França, foi criado o serviço CMP "Circuits Multi-Projets" envolvendo a UGA "Université Grenoble Alps", o Grenoble INP e o CNRS com o objetivo de proporcionar a fabricação de circuitos integrados monolíticos envolvendo vários projetos, de modo a reduzir os custos de desenvolvimento e de fabricação. O serviço CMP começou com a tecnologia de transístores NMOS de porta alinhada, com a regra de  $\lambda = 3 \mu m$  (dimensão mínima), especialmente vocacionada par realizar circuitos digitais.

Segundo Moore o número de transístores, na mesma área de circuito, duplicaria por ano.

<sup>&</sup>lt;sup>2</sup> Palo Alto Research Center.

Defense Advanced Research Projects Agency (EUA).

O Prof. José Alves Marques, professor do IST desde 1981, foi um dos primeiros investigadores do <u>INESC</u>, criado em 1980, tinha acabado o doutoramento na UGA, em França, sob orientação de François Anceau. Conjuntamente com o Prof Luis Vidigal, recém-chegado dos EUA, onde o ensino universitário do projeto de circuitos VLSI estava a florescer, também um dos primeiros investigadores do INESC, criaram a oportunidade de participar num dos primeiros projetos franceses do CMP 82.

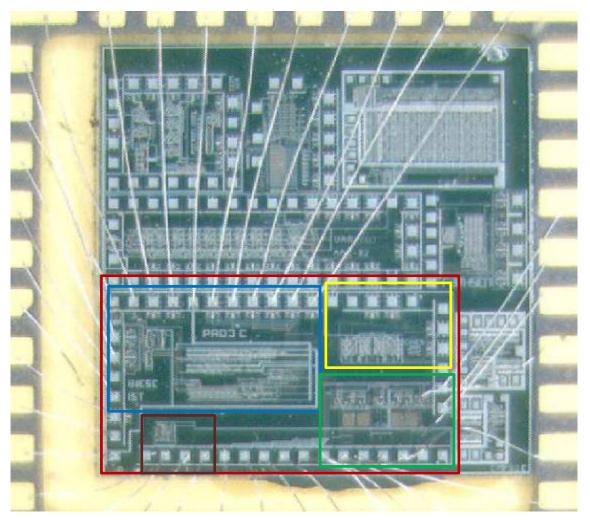

Surge, assim, em 1982, o primeiro circuito integrado monolítico VLSI com projetos concebidos em Portugal e em França. O circuito fabricado em França, chegou no início de 1983 e foram feitas as ligações do *chip* ao seu suporte, por *wire bonding* já em Portugal.

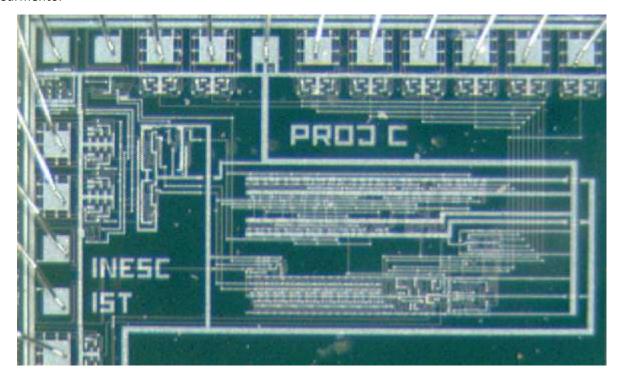

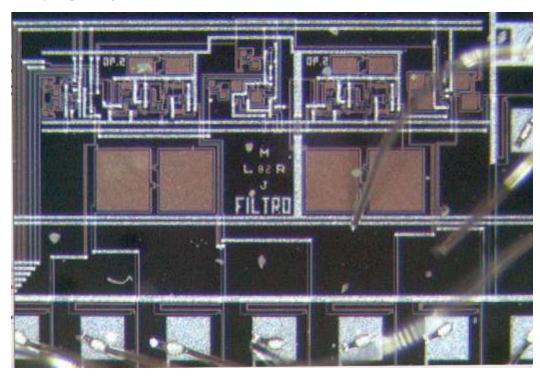

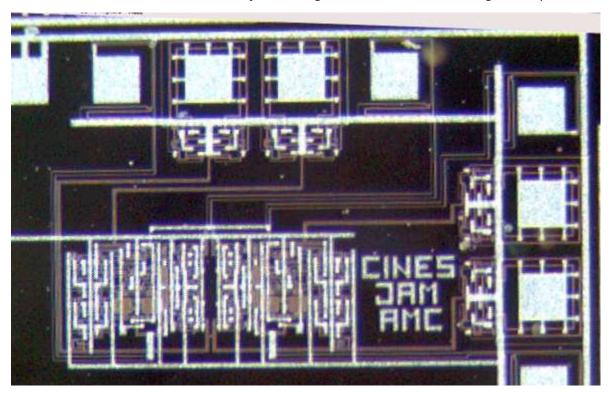

Os circuitos projetados em Portugal foram: o Projeto C, o projeto CINES, o Projeto Filtro e o projeto OP1.

Proj C – cor azul; Proj. CINES – cor amarelo; Proj. Filtro – cor verde; Proj. Opamp NMOS – cor castanho.

O projeto C foi liderado pelo Prof Mário Lança e consta de um circuito digital que formata uma trama PCM de 2 Mbps com 32 canais de áudio a 64 kbps. Este circuito exemplifica a enorme simplificação que um circuito integrado poderia trazer no sistema MIC 32, desenvolvido com circuitos digitais convencionais no CET, Centro de Estudos de Telecomunicações dos CTT, em Aveiro.

No projeto C participaram vários investigadores, nomeadamente, Prof. Mário Lança, Prof. Luis Vidigal e os estudantes de doutoramento Pedro Veiga, Carlos Almeida, Isabel Teixeira, Horácio Neto e Helena Sarmento.

O projeto Filtro e o projeto OP1, foram liderados por Moisés Piedade, na época estudante de doutoramento do IST, e foi um circuito de filtragem de 2ª ordem (filtro passa banda) com 300 Hz de largura de banda e frequência central de 1080 Hz. Neste projeto participaram: o Prof Luis Vidigal e os estudantes de pós-graduação Moisés Piedade, Rui Martins e João Freire.

O projeto CINES foi da responsabilidade do Prof. Alves Marques e do estudante de pós graduação Alberto Cunha. Consistiu num circuito de sincronização de relógios dentro de um circuito digital complexo.

O projeto OP1 foi um amplificador operacional, teoricamente de alto desempenho, realizado com transístores NMOS e foi realizado por Moisés Piedade, Rui Martins e João Freire.

#### As ferramentas de projeto

Na realização deste primeiro chip português as equipas encontraram enormes dificuldades pois não estavam disponíveis ferramentas de ajuda computacional que, hoje em dia, são correntes no projeto de circuitos integrados monolíticos.

Na simulação lógica usaram-se os simuladores desenvolvidos por investigadores do IST liderados pelo Prof. Mário Lança. Na simulação de circuitos analógicos usou-se o programa SPICE em que os modelos dos transístores tiveram de ser criados a partir da pequena informação disponível sobre a tecnologia NMOS que seria usada.

Na simulação dos circuitos com sinais amostrados usava-se a muito recente ferramenta SWITCAP desenvolvida por Fang e Tsividis na Columbia University (EUA) e também alguma experiência obtida a partir de alguns circuitos discretos com amplificadores operacionais, interruptores CMOS e condensadores desenvolvidos no CEAUTL<sup>4</sup> para realizar pequenos filtros.

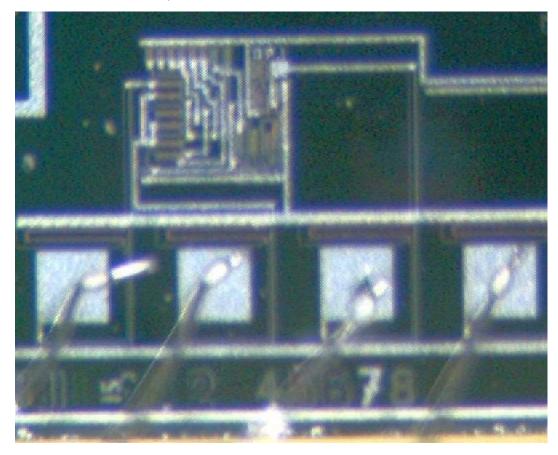

Como não estavam disponíveis ferramentas de edição computacional das plantas (layout) dos circuitos, estes eram previamente desenhados em folhas gigantes de papel quadriculado, obtidas por colagem de folhas em formato A3. Cada quadrado destas folhas equivalia à resolução de  $1\lambda$  (3  $\mu$ m) da tecnologia NMOS em que o circuito seria fabricado.

Os transístores eram desenhados com retângulos de cores que tinham correspondência com as diferentes fases do processo de fabricação. Respeitavam-se as regras de separação entre diferentes camadas do circuito por múltiplos de 1λ. As linhas condutoras metálicas (alumínio) eram constituídas por retângulos com a largura de 3λ.

Havia uma ferramenta computacional que apenas recebia a informação sobre retângulos com as coordenadas relativas à origem do circuito e as dimensões de comprimento e largura expressos em termos da unidade  $1\lambda$  e o tipo de camada a que se referia.

A planta de cada circuito era impressa, numa impressora gigante, a cores. As equipas faziam a verificação visual na planta se estavam todas as camadas que dariam origem a cada transístor NMOS, se os condutores estavam bem ligados e se havia alguma violação das regras de fabrico da tecnologia que iria ser usada.

Já depois de feita a fita magnética que transportaria toda a informação sobre os circuitos (*tape out*) para a fabricação em França, ter sido enviada e o processo de fabricação do CMP82 ter começado, recebemos um programa de verificação das plantas DRC<sup>5</sup> que extraía da planta os transístores e as ligações entre eles e, a partir disto, poderíamos verificar se correspondia aos esquemas elétricos pretendidos.

No projeto OP1 foi verificada a existência de um erro fatal. Um dos retângulos de condutor metálico tinha um comprimento maior do que devia de 2  $\lambda$  e isso infringia as regras de projeto e poderia provocar, na fabricação, um curto-circuito à massa a meio do caminho do sinal amplificado do OP1. E assim aconteceu, o OP1 não funcionou, mas todos os outros circuitos funcionaram.

## O ensino de tecnologias de fabrico dos circuitos integrados

O Prof. Luis Vidigal introduziu a disciplina VLSI de opção na licenciatura e no Mestrado. O Prof. Medeiros Silva começou a enfatizar o ensino das tecnologias integradas nas disciplinas de Eletrónica.

Em 1983, Moisés Piedade Introduziu, no curriculum de Eletrónica Aplicada III, disciplina obrigatória do Curso de Engenharia Eletrotécnica e Computadores, um capítulo sobre Técnicas de Projeto de Amplificadores Operacionais com tecnologias NMOS e CMOS.

-

<sup>&</sup>lt;sup>4</sup> Centro de Eletrónica Aplicada Universidade Técnica de Lisboa.

<sup>&</sup>lt;sup>5</sup> Design Rule Checker

Em 1984, Luis Vidigal e Moisés Piedade orientaramm trabalhos de realização de circuitos periféricos para Modem PSK 1200 b.p.s., utilizando circuitos com condensadores comutados e um circuito de condensadores comutados para síntese de voz, com a cooperação do Profs. Luís Borges de Almeida.

Seguiram-se outros projetos de circuitos integrados de DSPs e circuitos para telecomunicações liderados pelo Prof. Luis Vidigal.

Além destes projetos, o Prof. Luis Vidigal também envolveu alunos em processos de engenharia inversa sobre circuitos inovadores que estavam a aparecer no mercado de telecomunicações digitais. Estes circuitos eram observados ao microscópio e eram feitas fotografias de cada parte do circuito que depois eram juntas em enormes pósteres. Os alunos a partir das fotografias realizavam os esquemas elétricos dos circuitos do chip.

#### Referências

- [1] Robert W. Bower- "Insulated Gate Field Effect Transistors Fabricated Using the Gate as Source-Drain Mask" International Electron Device Meeting (IEDM),1966.

- [2] Mead and Connway, "Introduction to VLSI Systems", Addison-Wesley, 1980.

- [3] M. Lança, P. Veiga, C. Almeida, I.Teixeira, H. Neto e H. Sarmento, "Interface de Junção de 64 kbps para Sistema de Multiplexagem Mic32". *Textos das Sessões Técnicas do ENDIEL 83*, Lisboa, Janeiro de 1983.

- [4] M. Piedade, R. Martins, J. Freire, L. Vidigal, "Filtro Integrado Monolítico com Tecnologia NMOS", Textos das Sessões Técnicas do ENDIEL 83, Lisboa, Janeiro de 1983.

#### Nota:

A descrição detalhada dos circuitos portugueses realizados no IST e que estão incluídos neste primeiro circuito integrado será proximamente publicada na secção Historia da Tecnologia. no Museu faraday do IST,